VDD

RF<sub>OUT</sub>

$\overline{\mathsf{RF}_\mathsf{IN}}$

# 特点: 功能框图:

● 频率范围: 0.9~1.3GHz

● 增益: 典型值 20.0dB

● 噪声系数: 典型值 2.5dB

● 1dB 压缩点输出功率: 典型值+26.5dBm

● GaAs 裸片

● 芯片尺寸: 1.12×1.08×0.1mm

### 产品简介:

YDC1156 是一款采用 GaAs 工艺设计制造的低噪声放大器芯片。该芯片采用了片上金属化通孔工艺保证良好接地。芯片背面进行了金属化处理,适用于导电胶粘接或共晶烧结工艺,芯片均经过在片 100%直流与 RF 测试。

#### 性能参数: (50Ω系统)

|                     | 符号                | 测试条件                                            | 参数值      |       |       |             |     |      |

|---------------------|-------------------|-------------------------------------------------|----------|-------|-------|-------------|-----|------|

| 参数名称                |                   |                                                 | 常温(+25℃) |       | 全温    | 单位          | 备注  |      |

|                     |                   |                                                 | MIN      | TYP   | MAX   | -55℃~+85℃   |     |      |

| 频率范围                | f                 |                                                 | 0.9      | 1     | 1.3   | 0.9~1.3     | GHz | -    |

| 增益                  | G                 |                                                 | 19.0     | 20.0  | 21.5  | 18.5~22.5   | dB  | -    |

| 增益平坦度               | ΔG                | $V_{D} = +5.00V$                                | -        | 1.5   | 2.5   | ≤4.0        | dB  | -    |

| 输入驻波比               | VSWR <sub>I</sub> | f=0.9~1.3GHz                                    | -        | 1.4:1 | 1.8:1 | ≤2.0:1      | -   | -    |

| 输出驻波比               | VSWR <sub>O</sub> | P <sub>IN</sub> =-30dBm                         | -        | 1.6:1 | 2.0:1 | ≤2.0:1      | -   | -    |

| 噪声系数                | NF                |                                                 | -        | 2.5   | 3.2   | ≤3.7        | dB  | -    |

| 反向隔离度               | $I_R$             |                                                 | 28       | 30    | -     | ≥27         | dB  | -    |

| 1dB 压缩点输出功率         | OP <sub>1dB</sub> | V <sub>D</sub> =+5.00V                          | +25.5    | +26.5 | -     | ≥+25.0      | dBm | -    |

| 输出三阶截点 <sup>①</sup> | OIP <sub>3</sub>  | f=0.9~1.3GHz                                    | +35      | +38   | -     | ≥+30        | dBm | -    |

| 电源电压                | $V_{\mathrm{D}}$  | -                                               | +4.75    | +5.00 | +5.25 | +4.75~+5.25 | V   | 功能正常 |

| 工作电流                | $I_D$             | V <sub>D</sub> =+5.00V, P <sub>IN</sub> =-30dBm | -        | 200   | 210   | ≤240        | mA  | 静态电流 |

①输出三阶截点测试条件:双音信号间隔 1MHz,单音信号功率 0dBm。

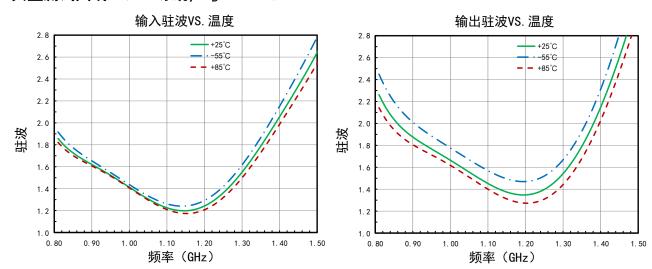

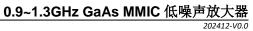

#### 典型测试曲线: (50Ω 系统, V<sub>D</sub>=+5.00V)

1. 20

频率(GHz)

1.30

1.40

1.50

20

0.80

0.90

1.00

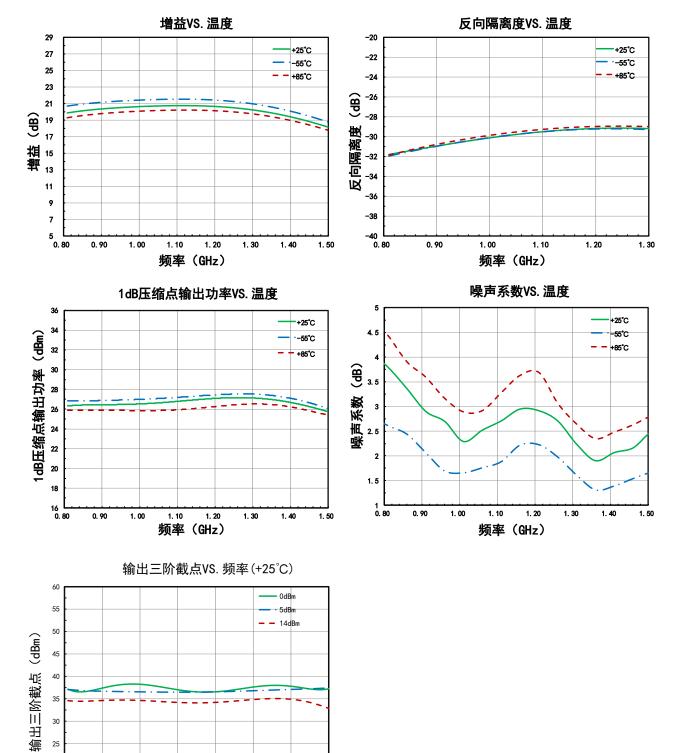

# 外形尺寸图:

注: 1.单位: mm;

- 2.芯片背面镀金:

- 3.键合压点镀金,尺寸: 0.1×0.1mm;

- 4.外形尺寸公差: ±0.05mm。

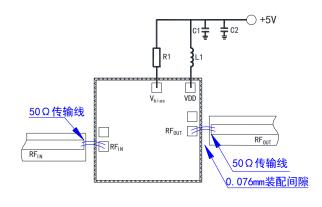

## 推荐装配图:

# 引脚定义:

| 符号                | 描述             |  |

|-------------------|----------------|--|

| $RF_{IN}$         | 射频输入,内部有隔直     |  |

| RF <sub>OUT</sub> | 射频输出,内部有隔直     |  |

| $V_{DD}$          | 电源端口,+5.00V 供电 |  |

| $V_{\rm bias}$    | 电流控制端口         |  |

| GND               | 接地             |  |

| 芯片背面              | 接地             |  |

### 极限参数表:

| 参数名称       | 极限值          |  |  |

|------------|--------------|--|--|

| 输入射频功率.50Ω | +15.5dBm     |  |  |

| 电源电压       | +6V          |  |  |

| 装配温度       | +300°C, 20s  |  |  |

| 工作温度       | -55°C∼+85°C  |  |  |

| 贮存温度       | -55°C∼+150°C |  |  |

| 静电放电敏感度等级  | 1A           |  |  |

超过以上任何一项极限参数,可能造成器件永久损坏。

## 推荐电路值:

| )  |          |    |  |  |

|----|----------|----|--|--|

| 位号 | 推荐值/推荐型号 | 备注 |  |  |

| C1 | 1000pF   | -  |  |  |

| C2 | 4.7uF    | -  |  |  |

| L1 | 8.2nH    | -  |  |  |

| R1 | 200 Ω    | -  |  |  |

注:分段使用时,根据使用频段调整隔直电容和馈电电感值。

注:射频端口应尽量靠近微带线以缩短键合金丝尺寸,典型的 装配间隙是 0.076~0.152mm, 使用Φ25um 双金丝键合, 建议 金丝长度 250~400um。

#### 产品使用注意事项:

- 1. 本芯片产品需要在干燥、氮气环境中存储,在超净环境装配使用。

- 2. 裸芯片使用的砷化镓材料较脆,芯片表面容易受损,不能用干或湿化学方法清洁芯片表面,使用时须小心。

- 3. 芯片粘结装配时,需考虑热膨胀应力对芯片的影响,芯片建议烧结或粘结在热膨胀系数相近的载体上,如可伐、钨铜 或钼铜垫片上,避免热膨胀应力匹配不当导致芯片开裂。

- 4. 芯片使用导电胶或合金烧结(合金温度不能超过300℃,时间不能超过20秒),使之充分接地。

- 5. 芯片射频端口使用 25um 双金丝键合,建议金丝长度 0.25~0.40mm (10~16 mils)。

- 6. 在存储和使用过程中注意防静电,烧结、键合台接地良好。